ANO 2020

FABIANO MENDES RIBEIRO | ESTUDO E CARACTERIZAÇÃO L INTERRUPOR DE GAN HEMT ATRAVÉS DO CIRCUITO DPT

CARACTERIZAÇÃO DO

UNIVERSIDADE DO ESTADO DE SANTA CATARINA – UDESC

CENTRO DE CIÊNCIAS TECNOLÓGICAS - CCT PROGRAMA DE PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA - PPGEEL

DISSERTAÇÃO DE MESTRADO

ESTUDO E CARACTERIZAÇÃO DO INTERRUPTOR DE GAN HEMT ATRAVÉS DO CIRCUITO DPT

**FABIANO MENDES RIBEIRO**

JOINVILLE, 2020

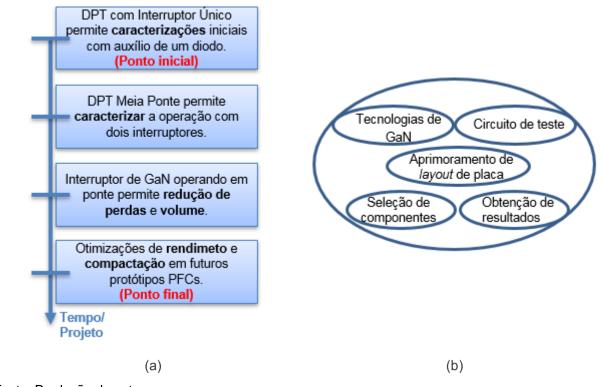

O presente trabalho compreende o estudo teórico e o desenvolvimento do protótipo DPT para caracterização do interruptor de GaN. Os principais tipos de interruptores de GaN são apresentados. O estado da arte é abordado com foco na exposição dos tipos do interruptor de GaN, buscando-se principalmente um apanhado geral nas referências de origem. O conceitual do circuito DPT e a forma como o circuito é utilizado para os testes do interruptor são mencionados. O layout do protótipo é desenvolvido e os componentes são selecionados na busca de um protótipo funcional. O protótipo é submetido aos testes iniciais e paralelamente é desenvolvido um estudo de possíveis melhorias nessa primeira versão. O estudo das parcelas de efeitos parasitas no layout da malha de potência do circuito DPT do primeiro protótipo é apresentado. Uma segunda versão de protótipo é mencionada, iuntamente com as melhorias aplicadas. Uma terceira versão de protótipo utilizando dois interruptores dispostos em conexão Meia Ponte é apresentada, juntamente com comparativos dos efeitos parasitas dos layouts das duas versões anteriores. Detalhes experimentais das operações de comando e potência executadas com níveis de tensão de 200 V e 400 V nos três protótipos são comentados. Testes nas proximidades dos limites do interruptor com níveis de tensão de 600 V e corrente de 50 A são mencionados. Por fim, é relatado o conjunto de várias transições turn-off e turn-on, para os níveis de tensão de 100 V, 200 V, 275 V e 400 V, e para níveis de corrente de 1 a 10 A.

Orientador: Yales Rômulo de Novaes

Joinville, 2020

### **FABIANO MENDES RIBEIRO**

# ESTUDO E CARACTERIZAÇÃO DO INTERRUPTOR DE GAN HEMT ATRAVÉS DO CIRCUITO DPT

Dissertação apresentada ao Programa de Pós-Graduação em Engenharia Elétrica do Centro de Ciências Tecnológicas da Universidade do Estado de Santa Catarina, como requisito parcial para a obtenção do grau de Mestre em Engenharia Elétrica.

Orientador: Prof. Dr. Yales Rômulo de Novaes

Ribeiro, Fabiano Mendes

Estudo e caracterização do interruptor de GaN HEMT através do circuito DPT / Fabiano Mendes Ribeiro. – Joinville, 2020.

186 p.: il.; 30 cm.

Orientador: Yales Rômulo de Novaes

Dissertação (Mestrado) – Universidade do Estado de Santa Catarina, Centro de Ciências Tecnológicas, Programa de Pós–Graduação em Engenharia Elétrica, Joinville, 2020.

1. Interruptor de GaN. 2. DPT. 3. Caracterização de Interruptor. I. Rômulo de Novaes, Yales . II. Universidade do Estado de Santa Catarina, Centro de Ciências Tecnológicas, Programa de Pós–Graduação em Engenharia Elétrica. III. Título

## Estudo e Caracterização do Interruptor de Gan através do Circuito DPT

por

#### Fabiano Mendes Ribeiro

Esta dissertação foi julgada adequada para obtenção do título de

## MESTRE EM ENGENHARIA ELÉTRICA

Área de concentração em "Sistemas Eletroeletrônicos" e aprovada em sua forma final pelo

CURSO DE MESTRADO ACADÊMICO EM ENGENHARIA ELÉTRICA

DO CENTRO DE CIÊNCIAS TECNOLÓGICAS DA

UNIVERSIDADE DO ESTADO DE SANTA CATARINA.

Banca Examinadora:

Prof. Dr. Yales Rômulo de Novaes

CCT/UDESC

(Orientador/Presidente)

Prof. Dr. Sérgió Vidal Garcia Oliveira CCT/UDESC

A video conference

Prof. Dr. Diego Santøs Steff

UFSC-Joinville

Joinville, SC, 27 de fevereiro de 2020.

| minha amada Yasmim Ro<br>o e Maria de Lourdes Venê<br>apesar de inúmeras di | ra, apoiaram-me incond |  |

|-----------------------------------------------------------------------------|------------------------|--|

|                                                                             | ra, apoiaram-me incond |  |

| o e Maria de Lourdes Venê                                                   | ra, apoiaram-me incond |  |

| o e Maria de Lourdes Venê                                                   | ra, apoiaram-me incond |  |

| o e Maria de Lourdes Venê                                                   | ra, apoiaram-me incond |  |

| o e Maria de Lourdes Venê                                                   | ra, apoiaram-me incond |  |

| o e Maria de Lourdes Venê                                                   | ra, apoiaram-me incond |  |

#### **AGRADECIMENTOS**

Aos meus amados pais e à minha amada noiva, pela paciência e gigantesca contribuição, apoiando-me nestes últimos anos de forma inimaginável.

Ao professor Yales Rômulo de Novaes, por me orientar e compartilhar o seu conhecimento. Além de grande professor, um ser humano incrível, incansavelmente transformando as minhas dificuldades e limitações em forças para prosseguirmos.

Ao professor Sérgio Vidal Garcia Oliveira, por contribuir ao meu trabalho principalmente nas reuniões de acompanhamento e nos processos de aquisição dos materiais.

Aos engenheiros Douglas e Gustavo, pelas contribuições ao meu trabalho principalmente nas reuniões de acompanhamento e pelos auxílios proporcionados pela parceria entre a UDESC e a empresa EMBRACO.

Aos colegas Rodrigo, Eduardo e Leandro, por muitos compartilhamentos de conhecimentos ao longo do presente trabalho.

Aos demais professores e colegas do Núcleo de Processamento de Energia Elétrica (nPEE) e Programa de Pós-Graduação em Engenharia Elétrica (PPGEEL) da UDESC, pelas contribuições de forma direta ou indiretamente à minha formação, nas disciplinas cursadas e no desenvolvimento deste projeto.

Ao Conselho Nacional de Desenvolvimento Científico e Tecnológico (CNPQ), pelo apoio financeiro.

#### RESUMO

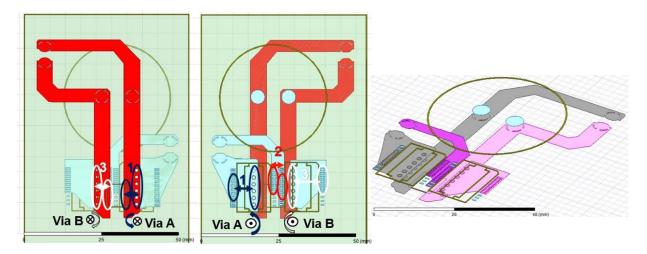

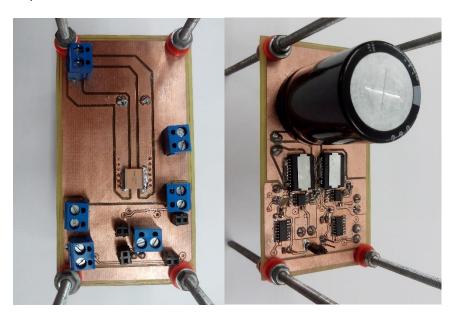

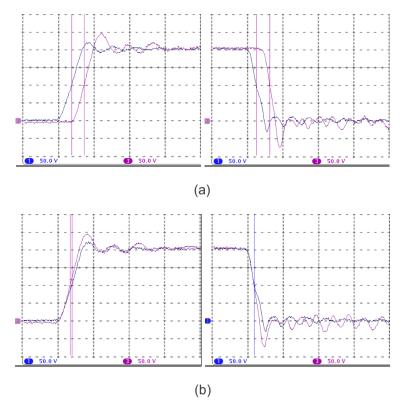

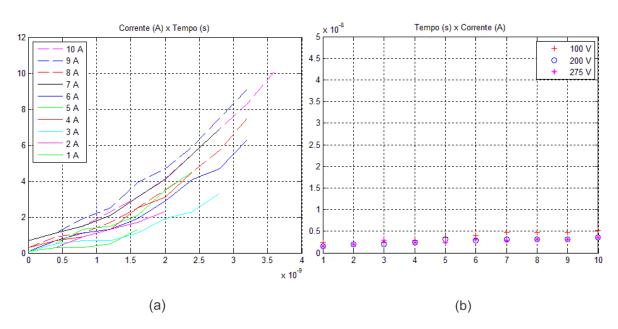

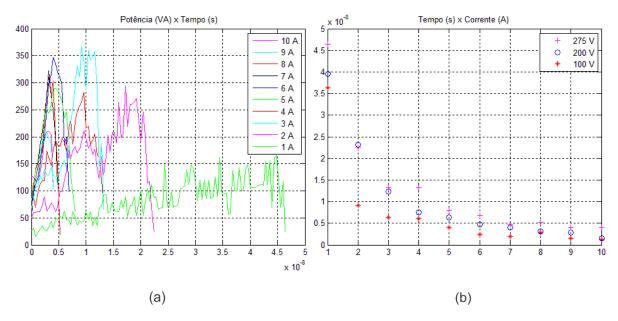

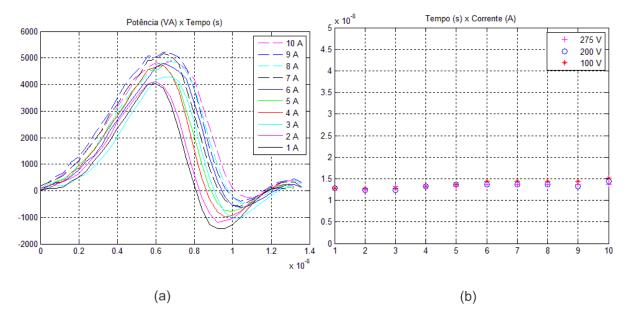

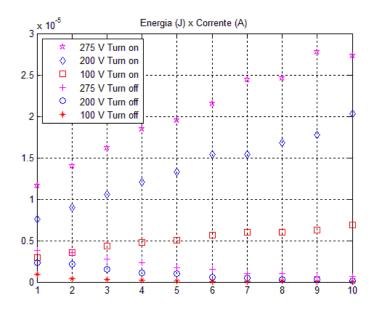

O presente trabalho compreende o estudo teórico e o desenvolvimento do protótipo DPT para caracterização do interruptor de GaN. Os principais tipos de interruptores de GaN são apresentados. O estado da arte é abordado com foco na exposição dos tipos do interruptor de GaN, buscando-se principalmente um apanhado geral nas referências de origem. O conceitual do circuito DPT e a forma como o circuito é utilizado para os testes do interruptor são mencionados. O *layout* do protótipo é desenvolvido e os componentes são selecionados na busca de um protótipo funcional. O protótipo é submetido aos testes iniciais e paralelamente é desenvolvido um estudo de possíveis melhorias nessa primeira versão. O estudo das parcelas de efeitos parasitas no layout da malha de potência do circuito DPT do primeiro protótipo é apresentado. Uma segunda versão de protótipo é mencionada, juntamente com as melhorias aplicadas. Uma terceira versão de protótipo utilizando dois interruptores dispostos em conexão Meia Ponte é apresentada, juntamente com comparativos dos efeitos parasitas dos layouts das duas versões anteriores. Detalhes experimentais das operações de comando e potência executadas com níveis de tensão de 200 V e 400 V nos três protótipos são comentados. Testes nas proximidades dos limites do interruptor com níveis de tensão de 600 V e corrente de 50 A são mencionados. Por fim, é relatado o conjunto de várias transições *turn-off* e *turn-on*, para os níveis de tensão de 100 V, 200 V, 275 V e 400 V, e para níveis de corrente de 1 a 10 A.

Palavras-chave: Interruptor de GaN. DPT. Caracterização de interruptor.

#### **ABSTRACT**

The present work comprises the theoretical study and the development of the DPT prototype to characterize the GaN switch. The main types of GaN switches are presented. The state of the art is approached with a focus on exposing the types of the GaN switch, seeking mainly a general overview of the references of origin. The conceptual of the DPT circuit and the way the circuit is used for switch tests are mentioned. The prototype layout is developed and the components are selected aiming a functional prototype. The prototype is subjected to initial tests and a study of possible improvements in this first version is developed in parallel. The study of the parasitic effects due to layout of the power loop of the DPT circuit of the first prototype is presented. A second prototype version is mentioned, along with the improvements applied. A third prototype version using two switches arranged in half a bridge connection is exposed, along with comparisons of the parasitic effects of the layouts of the two previous versions. Experimental details of the command and power operations performed with voltage levels of 200 V and 400 V over the three prototypes are commented. Tests in the vicinity of the switch limits with voltage levels of 600 V and current of 50 A are mentioned. Finally, the set of several turn-off and turn-on transitions is reported, for voltage levels of 100 V, 200 V, 275 V and 400 V, and for current levels from 1 to 10 A.

**Keywords**: GaN Switch. DPT. Switch characterization.

## LISTA DE ILUSTRAÇÕES

| Figura 1 – Relações com o presente trabalho: (a) motivação; (b) escopo30                                 |

|----------------------------------------------------------------------------------------------------------|

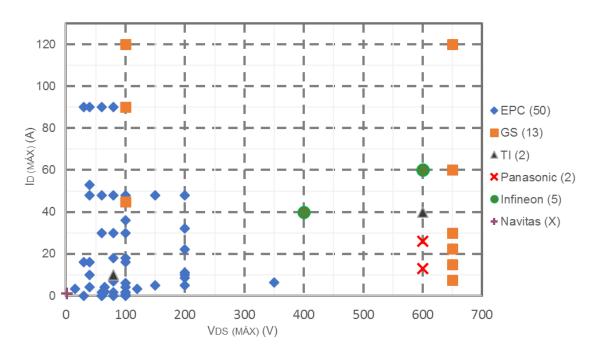

| Figura 2 – Modelos (2018) pesquisados/comercializados de dispositivos de GaN de                          |

| intensificação. Eixos: corrente $I_{d(\max)}$ e tensão de bloqueio $V_{ds(\max)}$ (sob                   |

| condições específicas)29                                                                                 |

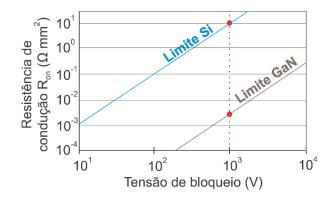

| Figura 3 – Limite teórico da resistência de condução em função da tensão de bloqueio                     |

| empregando os materiais Si e GaN31                                                                       |

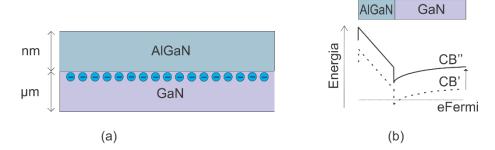

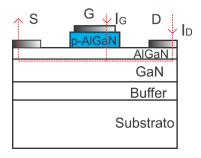

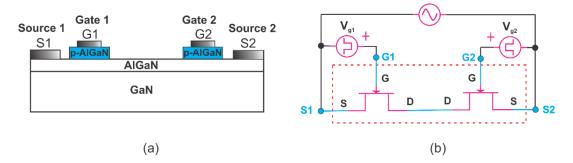

| Figura 4 – Estrutura AlGaN/GaN: (a) formação da região de 2DEG; (b) bandas de                            |

| condução dos tipos depleção e intensificação32                                                           |

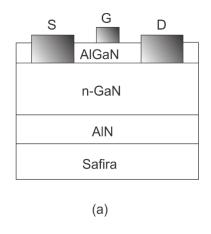

| Figura 5 – Depleção: (a) estrutura; (b) gráfico de $I_d \times V_{ds}$ obtido da estrutura para os       |

| valores de tensão $V_{_g}$ 34                                                                            |

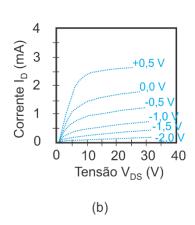

| Figura 6 – GaN HEMT: (a) estrutura AlGaN/GaN para obtenção de intensificação; (b)                        |

| gráfico de $I_d$ x $V_{ds}$ obtido da estrutura de intensificação para os valores de                     |

| tensão $_{V_g}$                                                                                          |

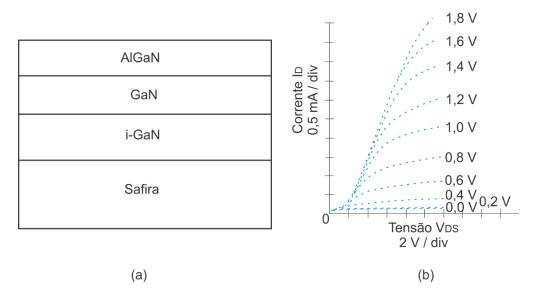

| Figura 7 – Estrutura <i>recessed-gate</i> com uma camada de AlGaN com menor                              |

| espessura sob o <i>gate</i> 37                                                                           |

| Figura 8 – Pontos experimentais e a curva de aproximação da tensão $V_{\scriptscriptstyle th}$ em função |

| da espessura do material AlGaN39                                                                         |

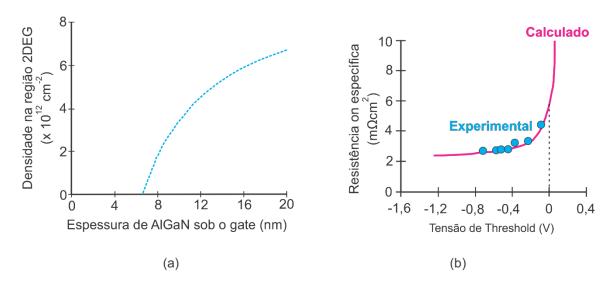

| Figura 9 – Estrutura <i>recessed-gate:</i> (a) curva da densidade da região 2DEG em                      |

| função da espessura da camada de AlGaN; (b) pontos experimentais e as                                    |

| curvas das resistências específicas em função da tensão $V_{th}$ 41                                      |

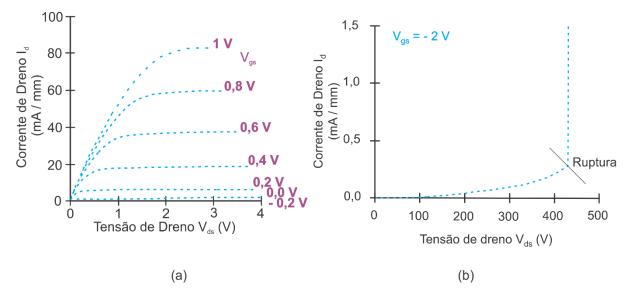

| Figura 10 – Característica estática: (a) curvas da corrente $I_d$ em função da tensão $V_{ds}$           |

| para vários valores da tensão $V_{_{gs}}$ ; (b) curva da corrente $I_{_d}$ em função da                  |

| tensão $V_{_{gs}}$ para a estrutura em bloqueio43                                                        |

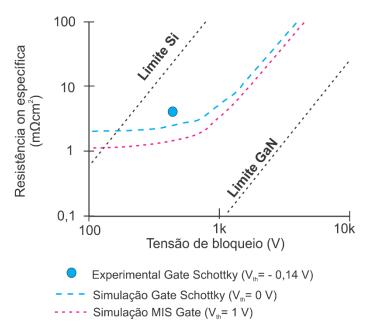

| Figura 11 – Curvas da resistência específica das estruturas em função da tensão de                       |

| bloqueio e ponto experimental <i>gate</i> Schottky44                                                     |

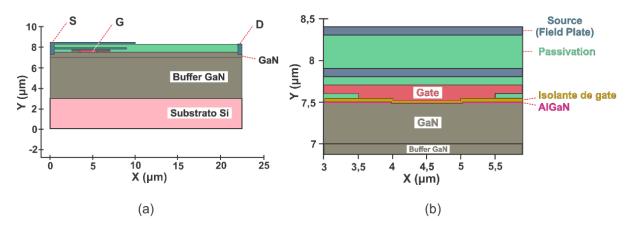

| Figura 12 – Modelo TCAD <i>recessed-gate</i> : (a) visão da estrutura; (b) visão ampliada da             |

| estrutura                                                                                                |

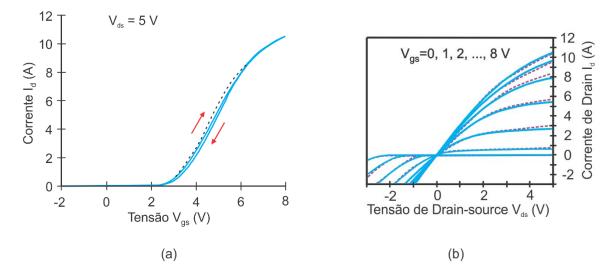

| Figura 13 – Comparativo <i>recessed-gate</i> : (a) curvas experimental (contínua) e                      |

| simulada (tracejada) da corrente $I_d$ em função da tensão $V_{gs}$ ; (b) curvas                         |

| a 	 gs 	 (                                                                                               |

| $\epsilon$  | experimentais (contínuas) e simuladas (tracejadas) da corrente $I_{\scriptscriptstyle d}$ em                                                                                                |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f           | unção da tensão $V_{\scriptscriptstyle ds}$ para tensões $V_{\scriptscriptstyle gs}$ 47                                                                                                     |

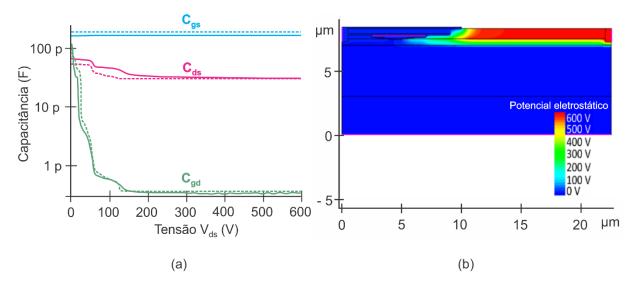

| (           | Estrutura <i>recessed-gate</i> : (a) curvas experimental (contínua) e simulada (tracejada) das capacitâncias da estrutura; (b) visão da distribuição do otencial eletrostático na estrutura |

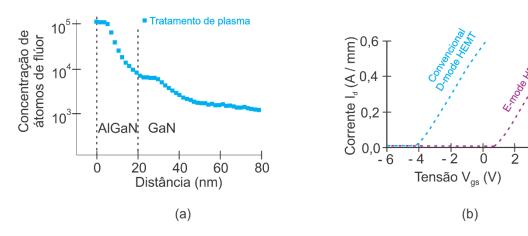

| Figura 15 – | Com base no tratamento de plasma: (a) concentração de fluoreto (b)                                                                                                                          |

| c           | curvas da corrente $I_{_d}$ em função da tensão $V_{_{gs}}$ para ambas as situações.49                                                                                                      |

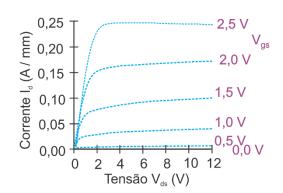

| Figura 16 – | Curvas da corrente $I_{_d}$ em função da tensão $V_{_{ds}}$ para várias tensões $V_{_{gs}}$ .50                                                                                             |

| Figura 18 – | Estrutura do transistor de injeção de <i>gate</i> (GIT)                                                                                                                                     |

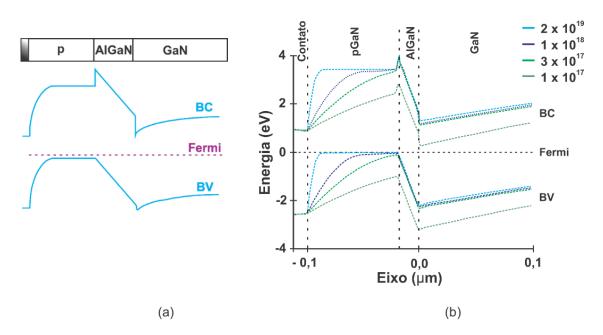

|             | · Diagrama de bandas da estrutura GIT: (a) para tensão de <i>gate</i> de 0 V; (b)<br>em função da dopagem do material pGaN53                                                                |

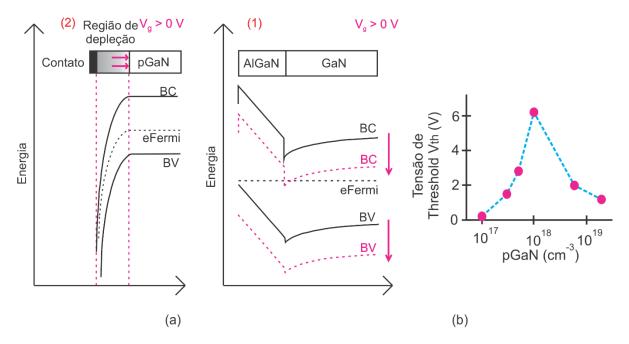

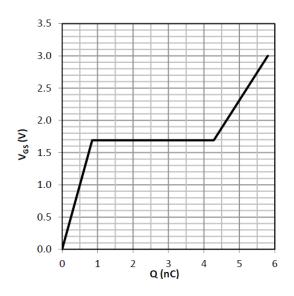

|             | · Ação de acionamento na estrutura GIT: (a) diagrama de bandas em                                                                                                                           |

| f           | unção da aplicação da tensão $V_{\scriptscriptstyle gs}$ ; (b) curva interligando os pontos                                                                                                 |

| a           | avaliados da tensão $V_{_{th}}$ em função da dopagem do material pGaN $\dots$ 54                                                                                                            |

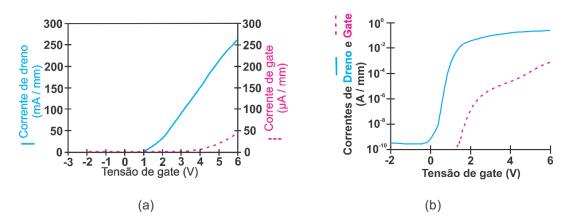

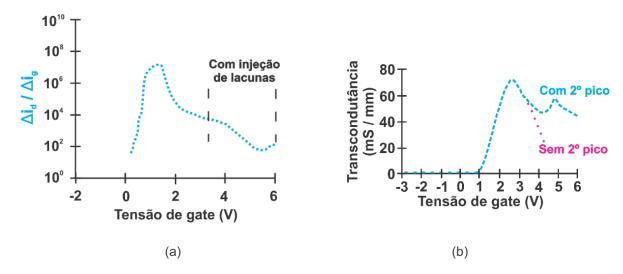

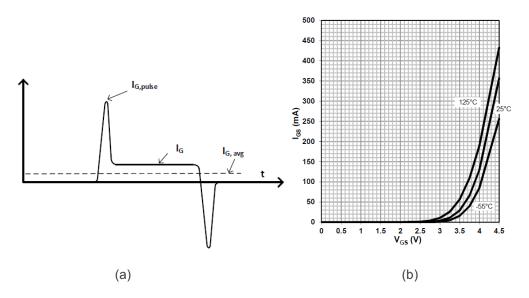

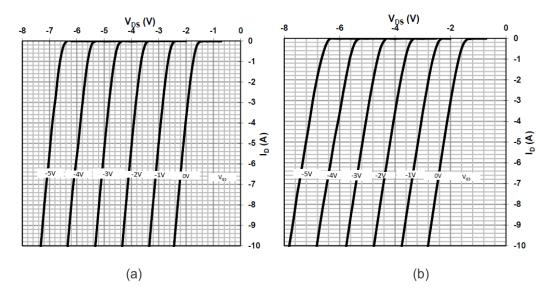

| Figura 21 – | - Gráfico das corrente $I_{\scriptscriptstyle d}$ e $I_{\scriptscriptstyle g}$ em função da tensão $V_{\scriptscriptstyle gs}$ da estrutura GIT: (a)                                        |

|             | com eixo das correntes linear; (b) com eixo das correntes logarítmico56. Trechos de operação: (a) curva $\Delta I_{_d}/\Delta I_{_g}$ em função da tensão $V_{_{gs}}$ ; (b)                 |

| C           | curvas da transcondutância com e sem 2º pico em função da tensão $V_{\scriptscriptstyle gs}$ . 57                                                                                           |

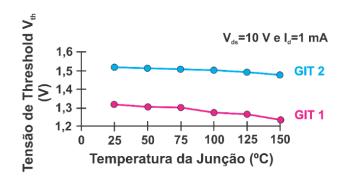

|             | - Pontos avaliados da tensão $V_{\scriptscriptstyle th}$ em função da temperatura57                                                                                                         |

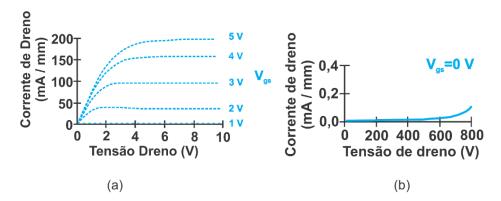

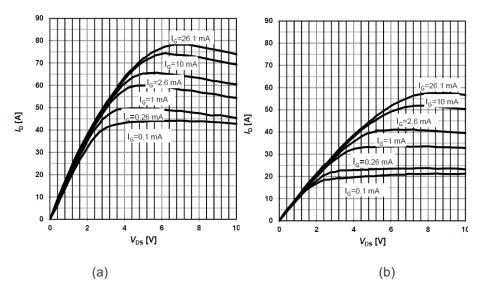

| Figura 24 – | - Curvas da corrente $I_{_d}$ em função da tensão $V_{_{ds}}$ para várias tensões $V_{_{gs}}$ :                                                                                             |

| Figura 25 – | (a) estado de condução; (b) estado de bloqueio                                                                                                                                              |

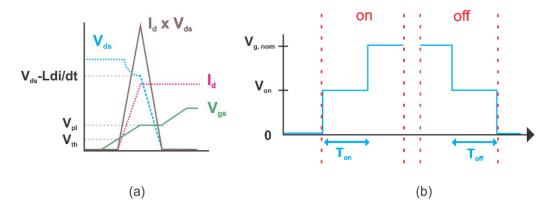

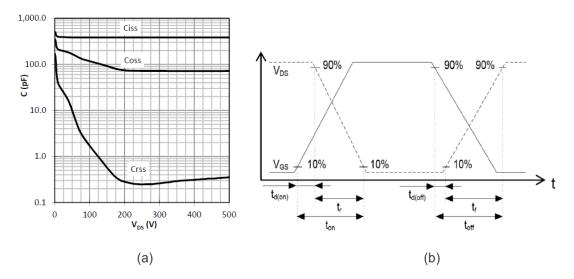

| te          | ensão $V_{ds}$ , corrente $I_{d}$ e tensão $V_{gs}$ ; (b) forma idealizada da tensão do $gate$                                                                                              |

|             | driver de dois níveis63                                                                                                                                                                     |

|             | Formas de onda: (a) turn-on; (b) turn-off64                                                                                                                                                 |

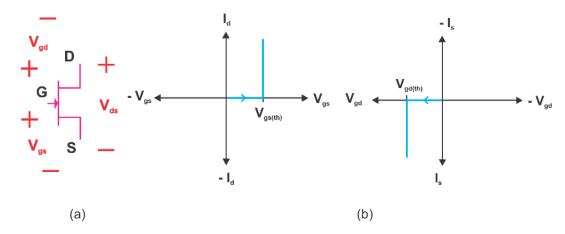

|             | - Acionamento do dispositivo: (a) tensões nos terminais do dispositivo: $V_{gs}$ ;                                                                                                          |

| Ţ           | $V_{gd}$ ; $V_{ds}$ ; (b) início da condução: (i) na forma direta quando $V_{gs}$ atinge $V_{gs(th)}$ ;                                                                                     |

| (           | (ii) na forma reversa quando $V_{ m gd}$ atinge $V_{ m gd(th)}$                                                                                                                             |

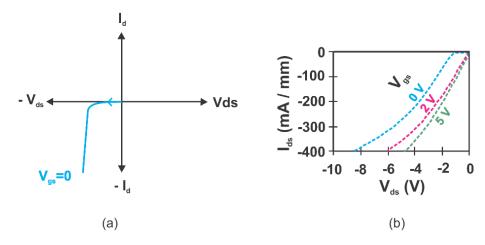

| Figura 29 | – Condução reversa $V_{sd}$ com aplicação de: (a) 0 V de tensão $V_{gs}$ ; (b) vários                                                                                                                                                                                                                                                                                                                                                                               |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | níveis de tensão $V_{gs}$ 66                                                                                                                                                                                                                                                                                                                                                                                                                                        |

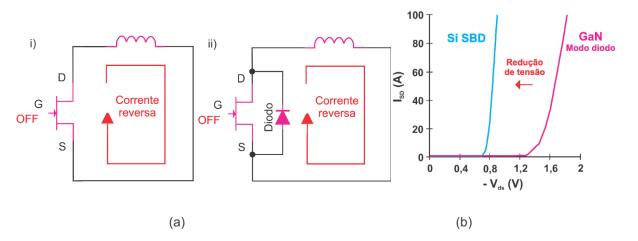

| Figura 30 | <ul> <li>Comparativo de condução reversa : (a) cicuito: (i) sem diodo, maior tensão reversa; (ii) com diodo, menor tensão reversa; (b) curvas de condução reversa do GaN HEMT e condução direta do diodo de barreira Schottky de sílicio.</li> </ul>                                                                                                                                                                                                                |

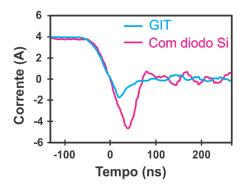

| Figura 31 | <ul> <li>Corrente de recuperação reversa do GaN HEMT e do diodo de<br/>recuperação rápida de Si.</li> </ul>                                                                                                                                                                                                                                                                                                                                                         |

| Figura 32 | <ul> <li>Dispositivo bidirecional: (a) estrutura; (b) analogia da estrutura interna</li> <li>com aplicação das tensões de gate</li></ul>                                                                                                                                                                                                                                                                                                                            |

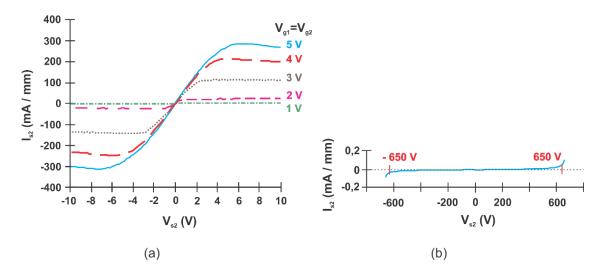

| Figura 33 | – Característica estática da estrutura bidirecional: (a) em condução com tensões $v_{g1}$ e $v_{g2}$ idênticas aplicadas aos pontos de $gate$ G1 e G2; (b)                                                                                                                                                                                                                                                                                                          |

| Figura 34 | bloqueio de tensão                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

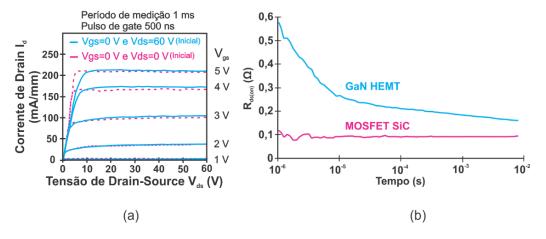

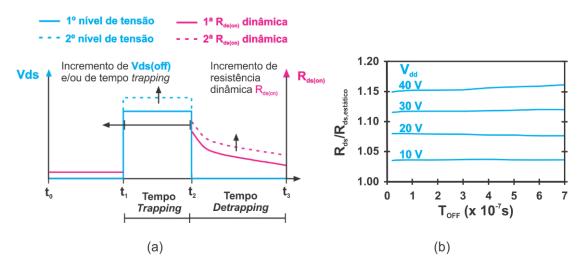

| Figura 35 | – Colapso de corrente: (a) curvas experimentais da corrente $I_d$ em função                                                                                                                                                                                                                                                                                                                                                                                         |

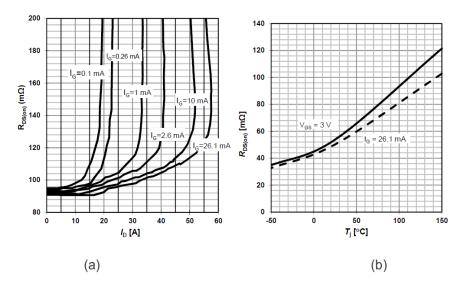

| Figura 36 | da tensão $V_{ds}$ para as tensões $V_{gs}$ . Curvas com aplicação da tensão $V_{ds}$ de 0 e 60 V antes de habilitar a condução; (b) resistência dinâmica72 – Colapso de corrente: (a) representação da variação da resistência dinâmica em função da variação de $V_{ds(off)}$ em bloqueio; (b) variação da resistência dinâmica (medido 2 $\mu$ s após o início da condução) em função da variação do valor de $V_{ds(off)}$ em bloqueio e do tempo de bloqueio73 |

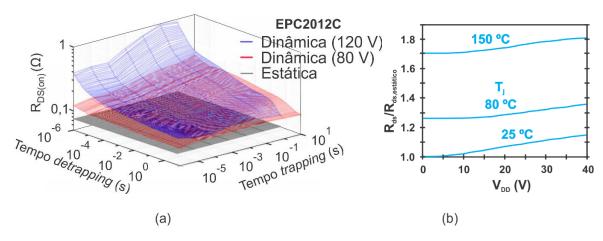

| Figura 37 | – Efeito $R_{ds(on)}$ : (a) valores estático e dinâmico; (b) variação da resistência dinâmica (medido 2 $\mu$ s após o início da condução) em função da temperatura e da tensão de bloqueio $V_{ds(off)}$ 74                                                                                                                                                                                                                                                        |

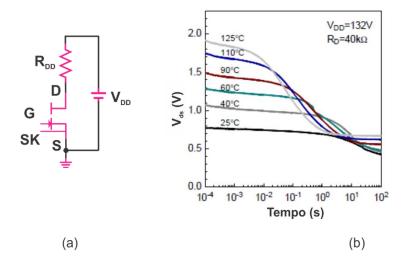

| Figura 38 | – Tensão de condução $V_{{\it ds(on)}}$ : (a) circuito para avaliação; (b) resultado em                                                                                                                                                                                                                                                                                                                                                                             |

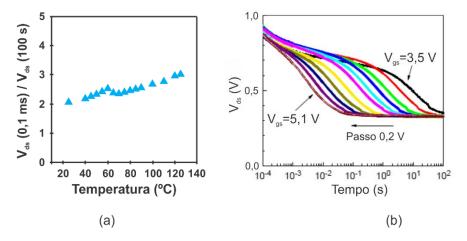

| Figura 39 | função do tempo de condução e para várias temperatura75 – Tensão $V_{\rm ds}$ durante a condução: (a) relação de tensão $V_{\rm ds}$ inicial e final                                                                                                                                                                                                                                                                                                                |

|           | (instantes de tempo: $10^{-4}$ s e $10^2$ s) em função da temperatura; (b) Tensão $V_{ds(on)}$ em função do tempo de recuperação para várias tensões $V_{gs}76$                                                                                                                                                                                                                                                                                                     |

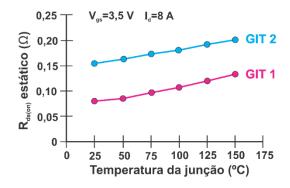

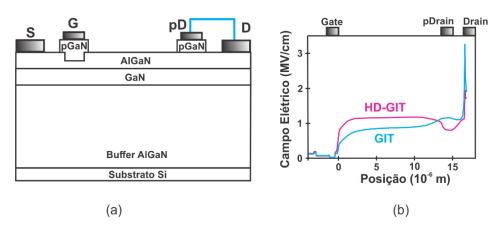

| Figura 40 – HD-GIT: (a) estrutura; (b) campo elétrico nas estruturas GIT e HD-GIT77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

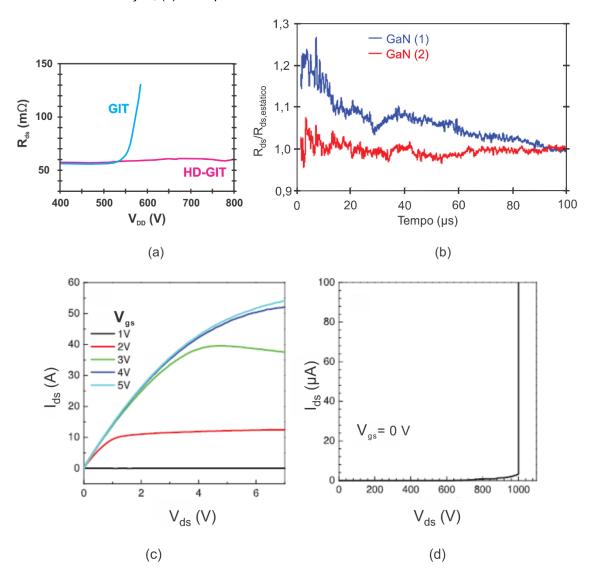

| Figura 41 – Curvas: (a) resistência de condução em função da tensão de bloqueio nas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| estruturas HD-GIT e GIT (medido 0,7 µs após o início da condução); (b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| resistência de condução (medido 1 µs após o início da condução) em                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| função do tempo para GIT (1) e HD-GIT (2); (c) característica estática da                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| condução; (d) e bloqueio HD-GIT78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

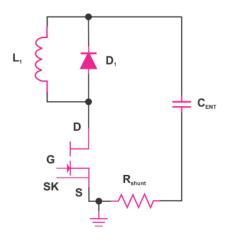

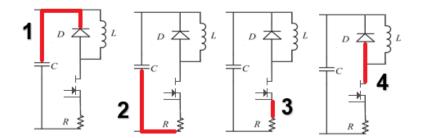

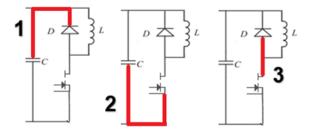

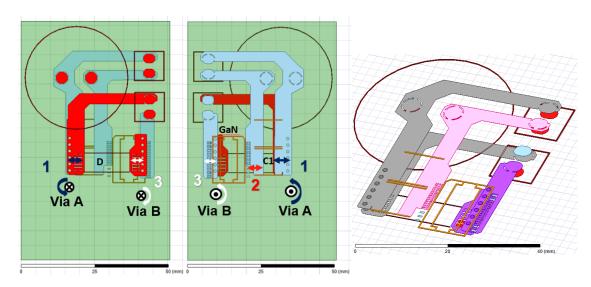

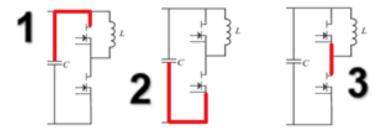

| Figura 42 – Circuito DPT80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Figura 43 – Circuito DPT: (a) intervalo de 0 a t0; (b) intervalo t0 a t1; (c) intervalo t1 a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| t2; (d) formas de onda da operação hard switching82                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Figura 44 – Circuito auxiliar para medição da tensão drain-source do dispositivo em                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| teste durante a condução com ponteiras de baixa tensão no ponto M83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

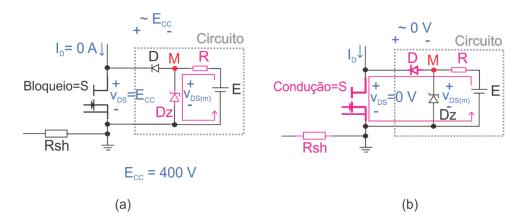

| Figura 45 – Circuito auxiliar para medição de tensão Vds: (a) interruptor bloqueado;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| (b) interruptor conduzindo84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

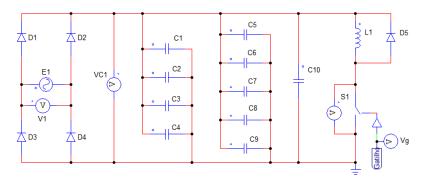

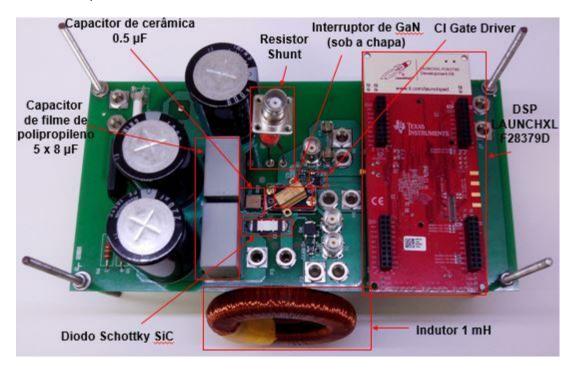

| Figura 46 – Circuito DPT ao teste                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

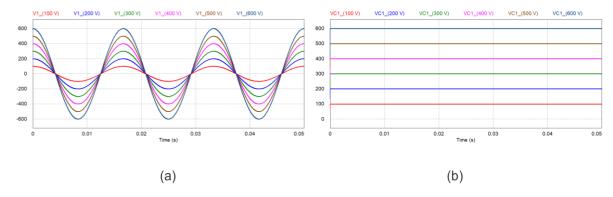

| Figura 47 – Forma de onda da tensão: (a) da fonte CA variável; (b) nos capacitores do                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| circuito DPT85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

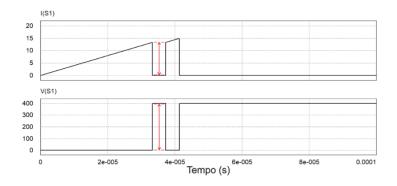

| Figura 48 – Forma de onda da corrente e da tensão no interruptor do circuito DPT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| com indicação dos instantes das transições de estados86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

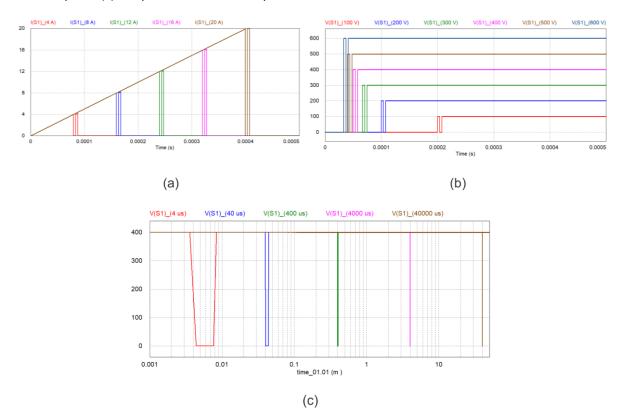

| Figura 49 – Valores alterados no teste do circuito DPT: (a) corrente de drain; (b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| tensão no estado de bloqueio; (c) tempo no estado de bloqueio87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

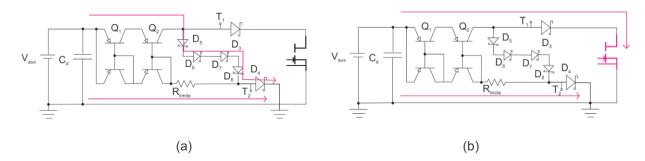

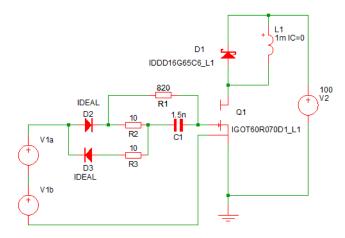

| Figura 50 – Circuito de simulação de componentes idealizados e modelos SPICE88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

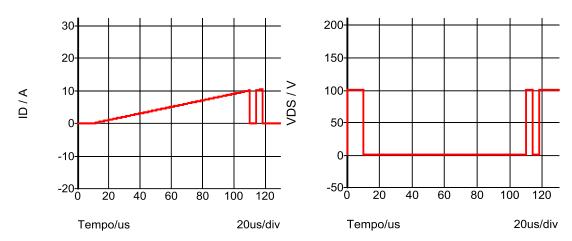

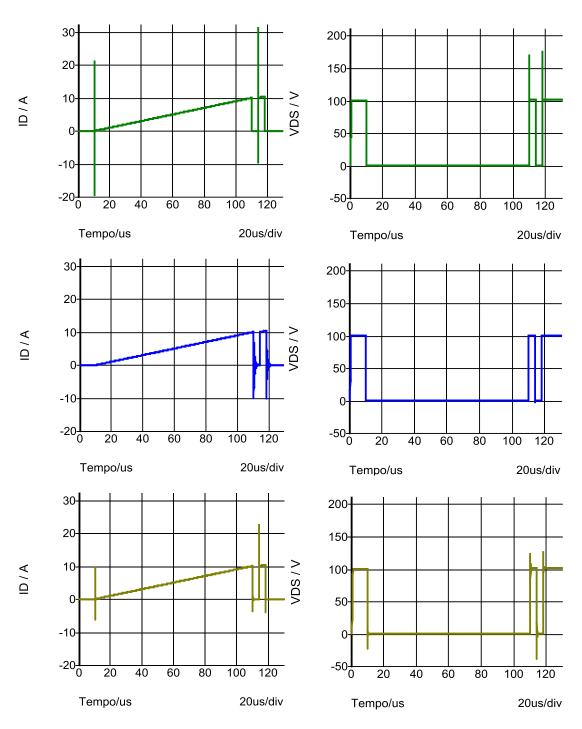

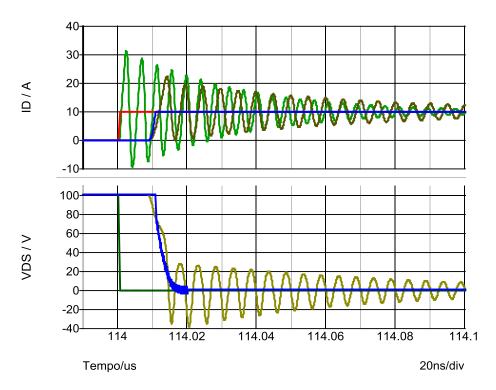

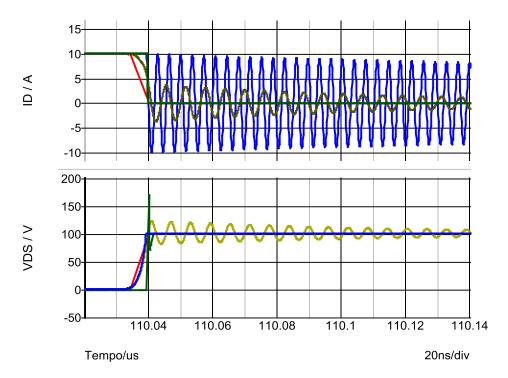

| Figura 51 – Formas de onda da corrente $i_d$ e da tensão $v_{ds}$ obtidas na simulação com:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| (a) Q1 e D1 ideais; (b) Q1 ideal e D1 modelo SPICE; (c) Q1 modelo SPICE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| e D1 ideal; (d) Q1 e D1 modelos SPICE89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Figura 52 – Detalhe da transição <i>turn-on</i> obtido nas simulações com Q1 ideal e D1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

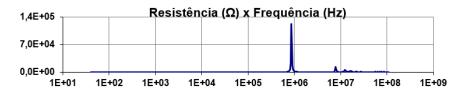

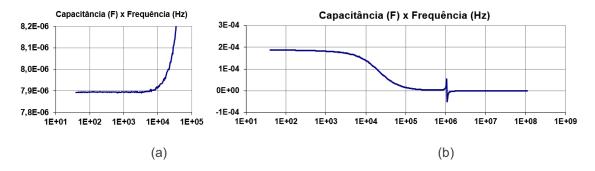

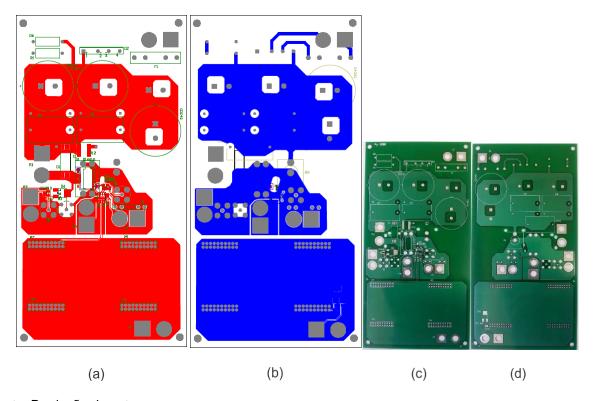

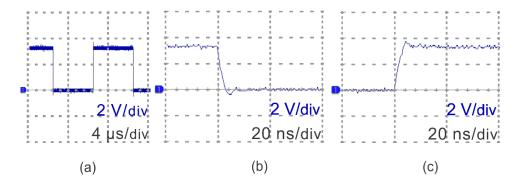

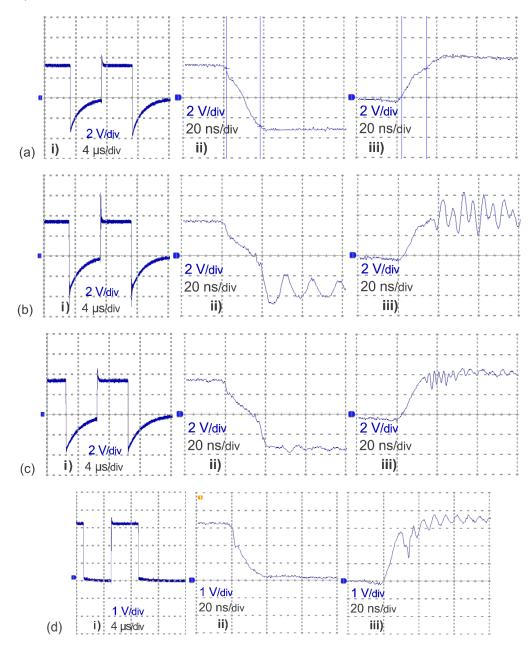

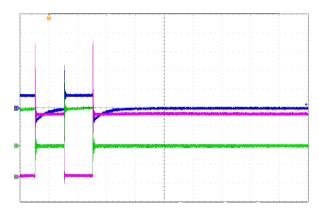

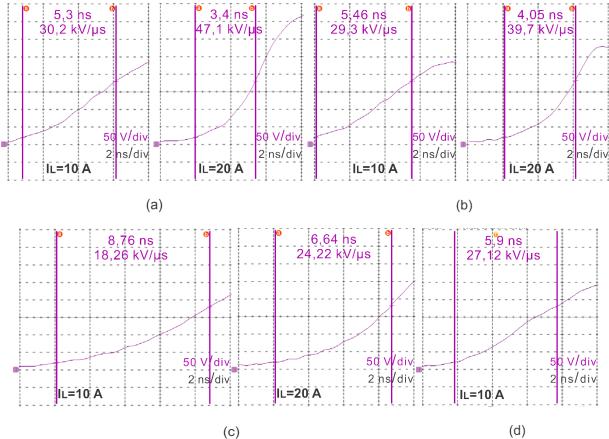

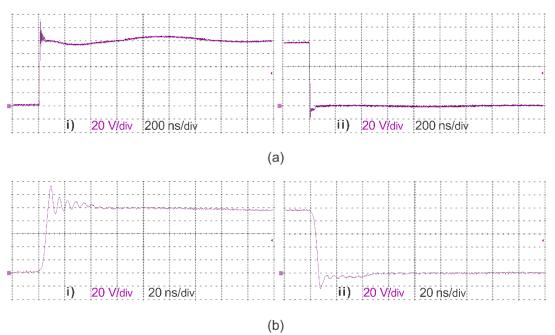

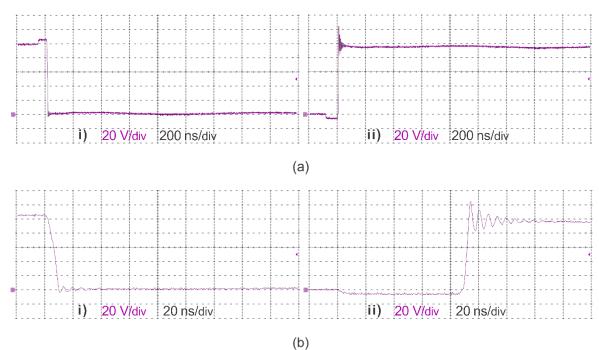

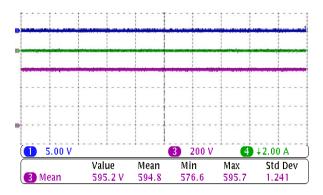

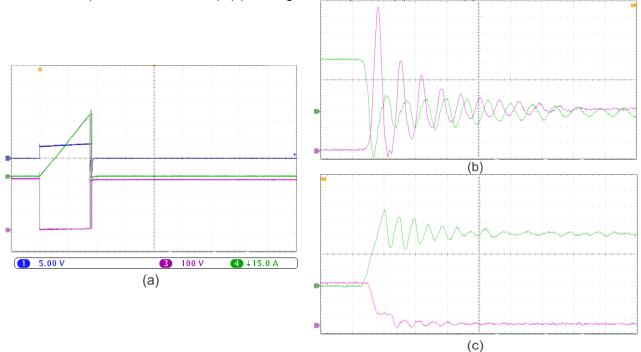

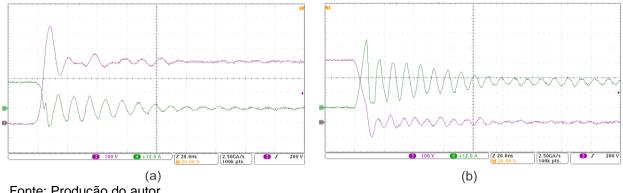

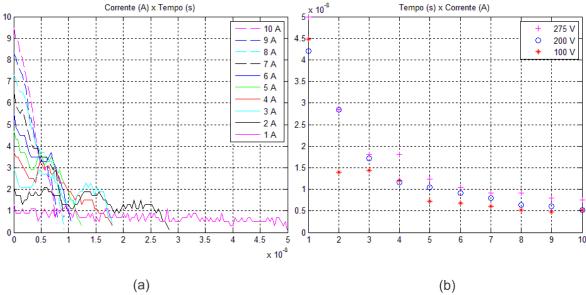

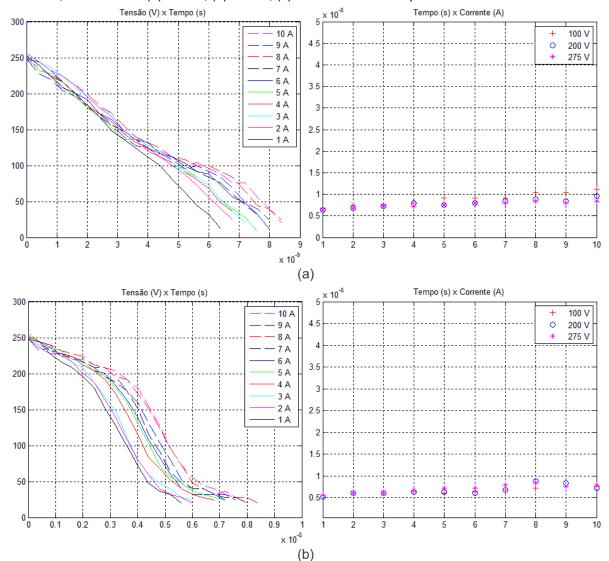

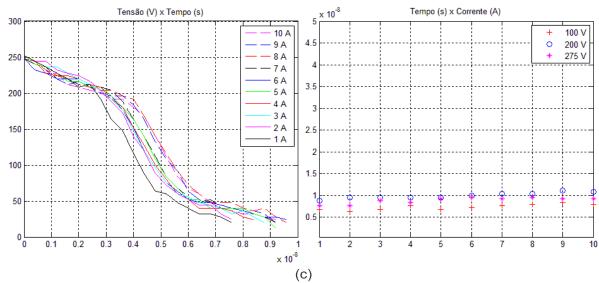

| ideal (vermelho), Q1 ideal e D1 Modelo SPICE (verde), Q1 modelo SPICE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |